INNOVATIVE INTEGRATION

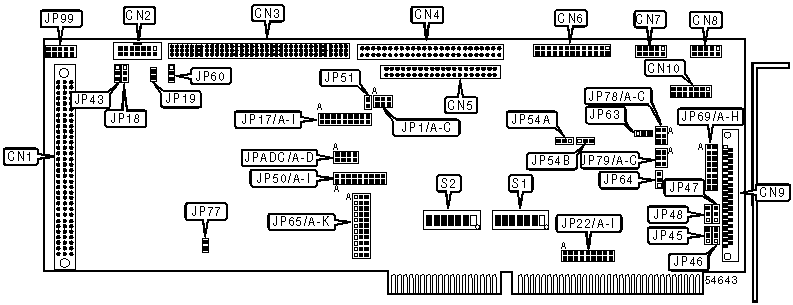

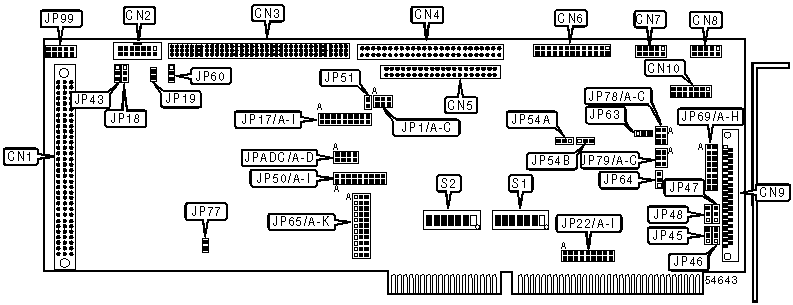

PC31

|

Card Type |

Digital I/O card |

|

I/O Options |

Digital I/O connector (2), analog I/O connector, memory expansion connector, DSPLINK expansion connector, |

|

Data Bus |

16-bit ISA |

|

Card Size |

Full-length, full-height card |

|

CONNECTIONS | |||

|

Function |

Label |

Function |

Label |

|

Unidentified |

CN1 |

26-pin digital I/O |

CN6 |

|

Unidentified |

CN2 |

10-pin serial port 1 - internal |

CN7 |

|

Memory expansion connector |

CN3 |

10-pin serial port 2 - internal |

CN8 |

|

DSPLINK expansion connector |

CN4 |

37-pin analog I/O |

CN9 |

|

50-pin digital I/O |

CN5 |

UART 2 breakout connector |

CN10 |

|

USER CONFIGURABLE SETTINGS | |||

|

Function |

Label |

Position | |

| » |

Zero wait states for onboard SRAM |

JP18 |

Open |

|

1 wait state for onboard SRAM |

JP18 |

Pins 1 & 2 closed | |

| » |

Onboard SRAM is 1 wait state or greater |

JP19 |

Open |

|

Onboard SRAM is 0 wait state |

JP19 |

Pins 1 & 2 closed | |

| » |

Less than 512kW SRAM installed |

JP43 |

Pins 1 & 2 closed |

|

512 kW SRAM installed |

JP43 |

Pins 2 & 3 closed | |

| » |

Factory configured - do not alter |

JP51 |

Unidentified |

| » |

Factory configured - do not alter |

JP60 |

Unidentified |

| » |

IN15 differential |

JP69/A |

Off |

|

IN15 single-ended |

JP69/A |

On | |

| » |

IN14 differential |

JP69/B |

Off |

|

IN14single-ended |

JP69/B |

On | |

| » |

IN13 differential |

JP69/C |

Off |

|

IN13 single-ended |

JP69/C |

On | |

| » |

IN11 differential |

JP69/E |

Off |

|

IN11 single-ended |

JP69/E |

On | |

| » |

IN12 differential |

JP69/D |

Off |

|

IN12 single-ended |

JP69/D |

On | |

| » |

IN10 differential |

JP69/F |

Off |

|

IN10 single-ended |

JP69/F |

On | |

| » |

IN9 differential |

JP69/G |

Off |

|

IN9 single-ended |

JP69/G |

On | |

| » |

IN8 differential |

JP69/H |

Off |

|

IN8 single-ended |

JP69/H |

On | |

| » |

Factory configured - do not alter |

JP78 |

Unidentified |

| » |

Factory configured - do not alter |

JP79 |

Unidentified |

| » |

Factory configured - do not alter |

JP99 |

Unidentified |

|

Note: JP69 can only be used if U99, U100, U101, and U102 are removed and JP63 and JP64 are configured with pins 2 & 3 closed. | |||

|

CLOCK SOURCE SELECTION | |||

|

Clock source |

JP1/A |

JP1/B |

JP1/C |

|

TMR1 clocked by H1/2 |

Open |

Open |

Closed |

|

TMR1 clocked externally |

Open |

Open |

Open |

|

TMR2 clocked by H1/2 |

Open |

Closed |

Open |

|

TMR2 clocked externally |

Open |

Open |

Open |

|

TMR3 clocked by H1/2 |

Closed |

Open |

Open |

|

TMR3 clocked externally |

Open |

Open |

Open |

|

OUTPUT SPAN SELECTION | ||||

|

Output span |

JP45 |

JP46 |

JP47 |

JP48 |

|

Bipolar +/-10v p-p |

Pins 1 & 2 closed |

Pins 1 & 2 closed |

Pins 1 & 2 closed |

Pins 1 & 2 closed |

|

Bipolar +/-1v p-p |

Pins 2 & 3 closed |

Pins 2 & 3 closed |

Pins 2 & 3 closed |

Pins 2 & 3 closed |

|

DATA WIDTH SELECTION | ||

|

Data width |

JP65/A-K |

JP77 |

|

16-bit |

Pins 2 & 3 closed |

Open |

|

32-bit |

Pins 1 & 2 closed |

Closed |

|

TRIGGER SOURCE SELECTION | ||||

|

Source |

JPADC/A |

JPADC/B |

JPADC/C |

JPADC/D |

|

External TMR0 |

Open |

Open |

Open |

Closed |

|

External TMR1 |

Open |

Open |

Closed |

Open |

|

Internal TCLK1 |

Open |

Closed |

Open |

Open |

|

Address strobe |

Closed |

Open |

Open |

Open |

|

STANDARD A/D INPUT RANGE SELECTION | ||

|

Input Span |

JP54A |

JP54B |

|

Channel A +/-10V |

Open |

N/A |

|

Channel A 0-10V |

Pins 1 & 2 closed |

N/A |

|

Channel A 10-0V |

Pins 2 & 3 closed |

N/A |

|

Channel B +/-10V |

N/A |

Open |

|

Channel B 0-10V |

N/A |

Pins 1 & 2 closed |

|

Channel B 10-0V |

N/A |

Pins 2 & 3 closed |

|

A/D INPUT TYPE SELECTION | ||

|

Mux type |

JP63 |

JP64 |

|

Channel A single ended |

Pins 2 & 3 closed |

N/A |

|

Channel A differential |

Pins 1 & 2 closed |

N/A |

|

Channel B single ended |

N/A |

Pins 2 & 3 closed |

|

Channel B differential |

N/A |

Pins 1 & 2 closed |

|

CONVERSION TRIGGER SOURCE DAC0/1 | |||||||||

|

Source |

JP50/A |

JP50/B |

JP50/C |

JP50/D |

JP50/E |

JP50/F |

JP50/G |

JP50/H |

JP50/I |

|

TRM0 |

Closed |

Open |

Open |

Open |

Open |

Open |

Open |

Open |

Open |

|

TRM1 |

Open |

Closed |

Open |

Open |

Open |

Open |

Open |

Open |

Open |

|

TCLK1 |

Open |

Open |

Closed |

Open |

Open |

Open |

Open |

Open |

Open |

|

0XFFF980 |

Open |

Open |

Open |

Closed |

Open |

Open |

Open |

Open |

Open |

|

CONVERSION TRIGGER SOURCE DAC2/3 | |||||||||

|

Source |

JP50/A |

JP50/B |

JP50/C |

JP50/D |

JP50/E |

JP50/F |

JP50/G |

JP50/H |

JP50/I |

|

TRM0 |

Open |

Open |

Open |

Open |

Closed |

Open |

Open |

Open |

Open |

|

TRM1 |

Open |

Open |

Open |

Open |

Open |

Closed |

Open |

Open |

Open |

|

TCLK1 |

Open |

Open |

Open |

Open |

Open |

Open |

Closed |

Open |

Open |

|

0XFFF980 |

Open |

Open |

Open |

Open |

Open |

Open |

Open |

Closed |

Open |

|

inverted version of DAC0/1 trigger pulse |

Open |

Open |

Open |

Open |

Open |

Open |

Open |

Open |

Closed |

|

INTERRUPT COMBINATION EI1 SELECTION | |||||||||

|

Source |

JP17/A |

JP17/B |

JP17/C |

JP17/D |

JP17/E |

JP17/F |

JP17/G |

JP17/H |

JP17/I |

|

8530 UART |

Open |

Open |

Open |

Open |

Open |

Open |

Open |

Open |

Closed |

|

DSPLINK INT0 |

Open |

Open |

Open |

Open |

Open |

Open |

Open |

Closed |

Open |

|

8254 TMR0 |

Open |

Open |

Open |

Open |

Open |

Open |

Closed |

Open |

Open |

|

INTERRUPT COMBINATION EI2 SELECTION | |||||||||

|

Source |

JP17/A |

JP17/B |

JP17/C |

JP17/D |

JP17/E |

JP17/F |

JP17/G |

JP17/H |

JP17/I |

|

8530 UART |

Open |

Open |

Open |

Open |

Open |

Closed |

Open |

Open |

Open |

|

’C31 TMR1 |

Open |

Open |

Open |

Open |

Closed |

Open |

Open |

Open |

Open |

|

PC_INT |

Open |

Open |

Open |

Closed |

Open |

Open |

Open |

Open |

Open |

|

INTERRUPT COMBINATION EI3 SELECTION | |||||||||

|

Source |

JP17/A |

JP17/B |

JP17/C |

JP17/D |

JP17/E |

JP17/F |

JP17/G |

JP17/H |

JP17/I |

|

8254 TMR2 |

Open |

Open |

Closed |

Open |

Open |

Open |

Open |

Open |

Open |

|

PC_MSG |

Open |

Closed |

Open |

Open |

Open |

Open |

Open |

Open |

Open |

|

/DSPLINK INT1 |

Closed |

Open |

Open |

Open |

Open |

Open |

Open |

Open |

Open |

|

I/O CONFIGURATION | |||||||

|

I/O address |

S1/1 |

S1/2 |

S1/3 |

S1/4 |

S1/5 |

S1/6 |

S1/7 |

|

200h |

Off |

On |

Off |

Off |

Off |

Off |

Off |

|

210h |

Off |

On |

Off |

Off |

Off |

Off |

On |

|

220h |

Off |

On |

Off |

Off |

Off |

On |

Off |

|

230h |

Off |

On |

Off |

Off |

Off |

On |

On |

|

240h |

Off |

On |

Off |

Off |

On |

Off |

Off |

|

250h |

Off |

On |

Off |

Off |

On |

Off |

On |

|

260h |

Off |

On |

Off |

Off |

On |

On |

Off |

|

270h |

Off |

On |

Off |

Off |

On |

On |

On |

|

280h |

Off |

On |

Off |

On |

Off |

Off |

Off |

|

290h |

Off |

On |

Off |

On |

Off |

Off |

On |

|

2A0h |

Off |

On |

Off |

On |

Off |

On |

Off |

|

2B0h |

Off |

On |

Off |

On |

Off |

On |

On |

|

2C0h |

Off |

On |

Off |

On |

On |

Off |

Off |

|

2D0h |

Off |

On |

Off |

On |

On |

Off |

On |

|

2E0h |

Off |

On |

Off |

On |

On |

On |

Off |

|

2F0h |

Off |

On |

Off |

On |

On |

On |

On |

|

300h |

Off |

On |

On |

Off |

Off |

Off |

Off |

|

310h |

Off |

On |

On |

Off |

Off |

Off |

On |

|

320h |

Off |

On |

On |

Off |

Off |

On |

Off |

|

330h |

Off |

On |

On |

Off |

Off |

On |

On |

|

340h |

Off |

On |

On |

Off |

On |

Off |

Off |

|

350h |

Off |

On |

On |

Off |

On |

Off |

On |

|

360h |

Off |

On |

On |

Off |

On |

On |

Off |

|

370h |

Off |

On |

On |

Off |

On |

On |

On |

|

380h |

Off |

On |

On |

On |

Off |

Off |

Off |

|

390h |

Off |

On |

On |

On |

Off |

Off |

On |

|

3A0h |

Off |

On |

On |

On |

Off |

On |

Off |

|

3B0h |

Off |

On |

On |

On |

Off |

On |

On |

|

3C0h |

Off |

On |

On |

On |

On |

Off |

Off |

|

3D0h |

Off |

On |

On |

On |

On |

Off |

On |

|

3E0h |

Off |

On |

On |

On |

On |

On |

Off |

|

3F0h |

Off |

On |

On |

On |

On |

On |

On |

|

DUAL PORT RAM CONFIGURATION | ||||||||

|

Address |

S2/1 |

S2/2 |

S2/3 |

S2/4 |

S2/5 |

S2/6 |

S2/7 |

S2/8 |

|

C000:0000h |

Off |

On |

On |

Off |

Off |

Off |

Off |

Off |

|

C000:4000h |

Off |

On |

On |

Off |

Off |

Off |

On |

Off |

|

C000:8000h |

Off |

On |

On |

Off |

Off |

On |

Off |

Off |

|

C000:C000h |

Off |

On |

On |

Off |

Off |

On |

On |

Off |

|

D000:0000h |

Off |

On |

On |

Off |

On |

Off |

Off |

Off |

|

D000:4000h |

Off |

On |

On |

Off |

On |

Off |

On |

Off |

|

D000:8000h |

Off |

On |

On |

Off |

On |

On |

Off |

Off |

|

D000:C000h |

Off |

On |

On |

Off |

On |

On |

On |

Off |

|

INTERRUPT SELECTION | |||||||||

|

Setting |

JP22/A |

JP22/B |

JP22/C |

JP22/D |

JP22/E |

JP22/F |

JP22/G |

JP22/H |

JP22/I |

|

IRQ3 |

Closed |

Open |

Open |

Open |

Open |

Open |

Open |

Open |

Open |

|

IRQ4 |

Open |

Closed |

Open |

Open |

Open |

Open |

Open |

Open |

Open |

|

IRQ5 |

Open |

Open |

Closed |

Open |

Open |

Open |

Open |

Open |

Open |

|

IRQ7 |

Open |

Open |

Open |

Closed |

Open |

Open |

Open |

Open |

Open |

|

IRQ9 |

Open |

Open |

Open |

Open |

Closed |

Open |

Open |

Open |

Open |

|

IRQ10 |

Open |

Open |

Open |

Open |

Open |

Closed |

Open |

Open |

Open |

|

IRQ11 |

Open |

Open |

Open |

Open |

Open |

Open |

Closed |

Open |

Open |

|

IRQ12 |

Open |

Open |

Open |

Open |

Open |

Open |

Open |

Closed |

Open |

|

IRQ15 |

Open |

Open |

Open |

Open |

Open |

Open |

Open |

Open |

Closed |

|

MISCELLANEOUS TECHNICAL NOTES |

|

The PC31 uses a 32-bit Digital Signal Processor as a coprocessor. This processor addresses memory in 32-bit chunks called "words". |